ASIC Verification Engineer Resume Guide

ASIC verification engineers design and verify integrated circuits to ensure they meet a specified set of requirements. They also analyze, troubleshoot, and debug designs in order to improve the performance of the circuit. Additionally, they develop simulation models and testbenches for verifying the functionality of ASICs before manufacturing them.

You have the knowledge and expertise to be a great asset to any team of ASIC verification engineers. But before you can get your foot in the door, you must write an impressive resume that will catch employers’ attention.

This guide will walk you through the entire process of creating a top-notch resume. We first show you a complete example and then break down what each resume section should look like.

Table of Contents

The guide is divided into sections for your convenience. You can read it from beginning to end or use the table of contents below to jump to a specific part.

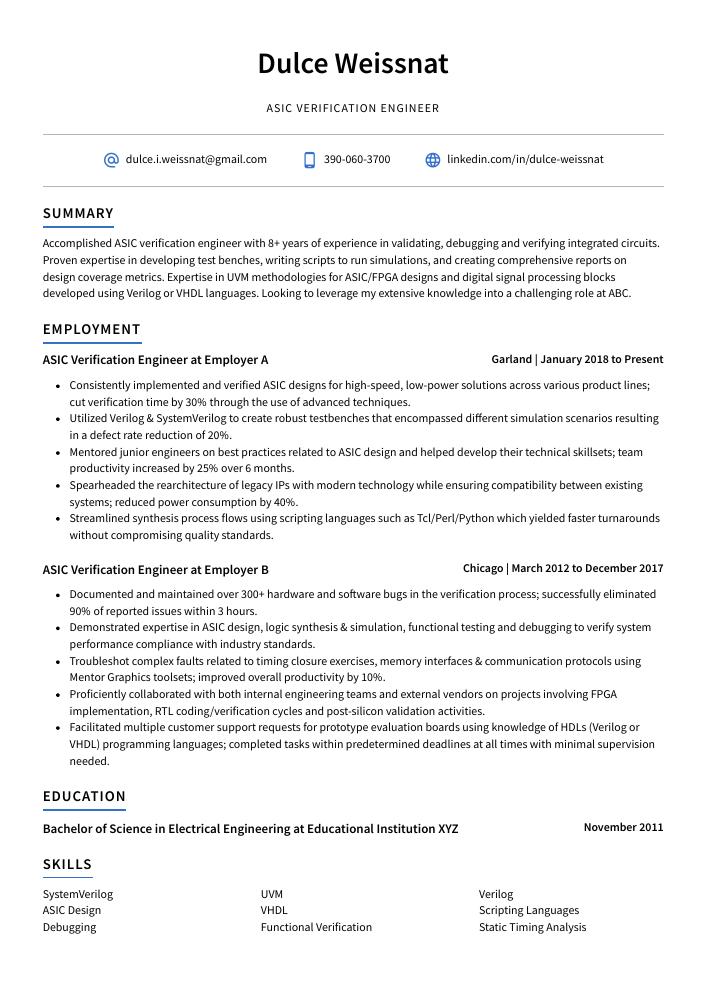

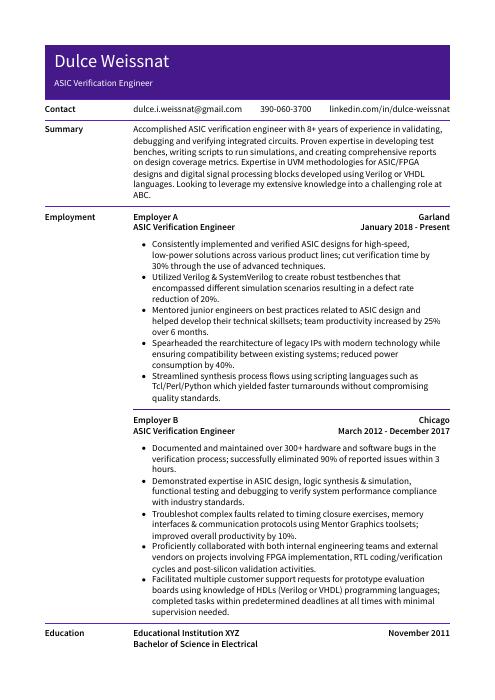

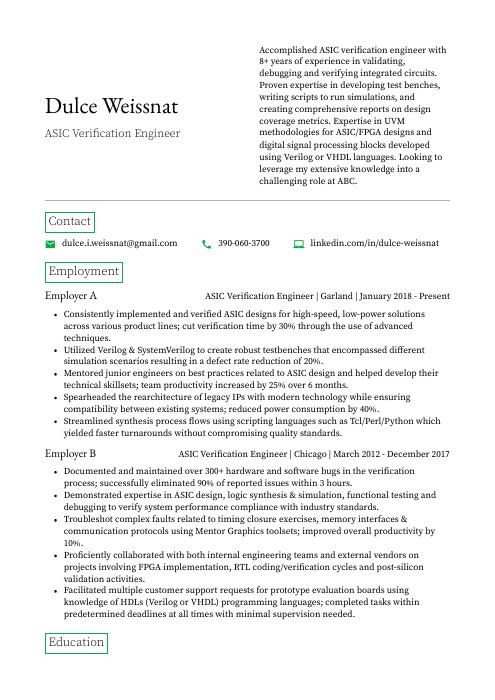

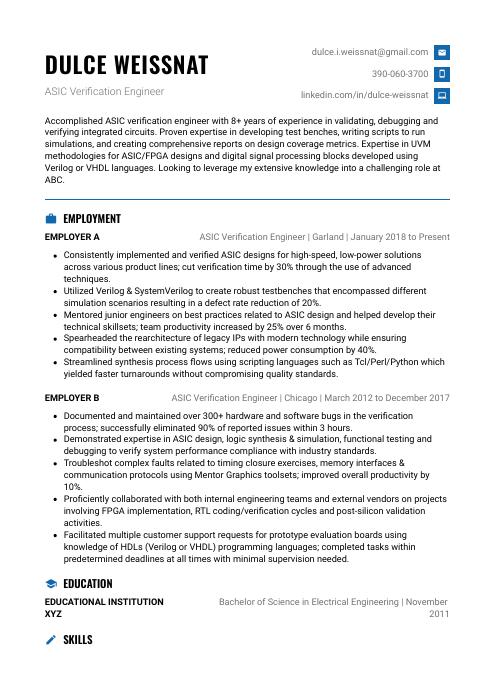

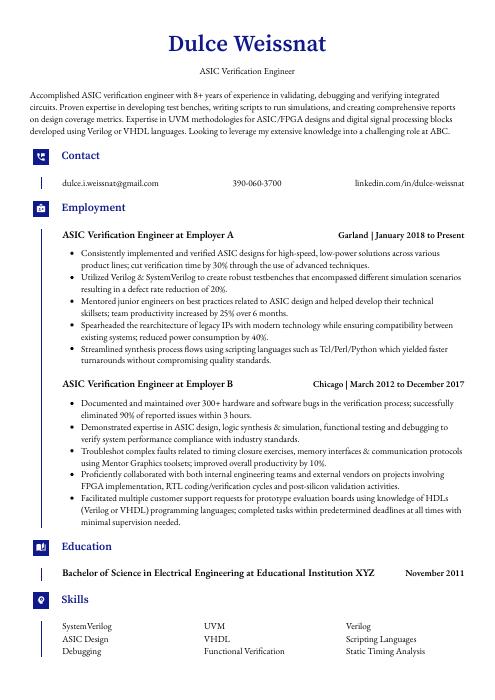

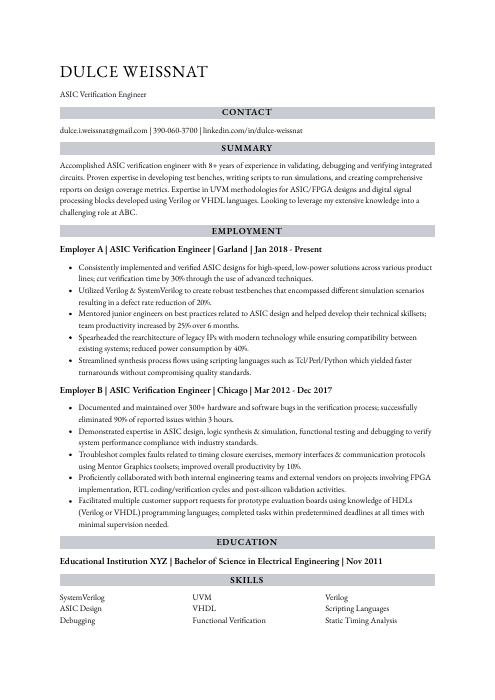

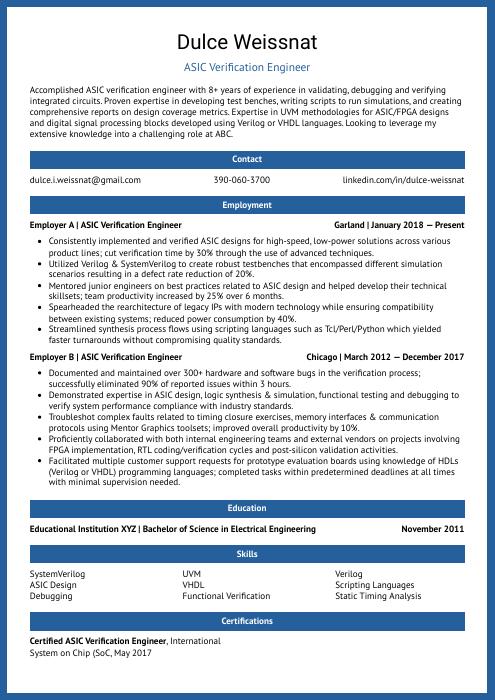

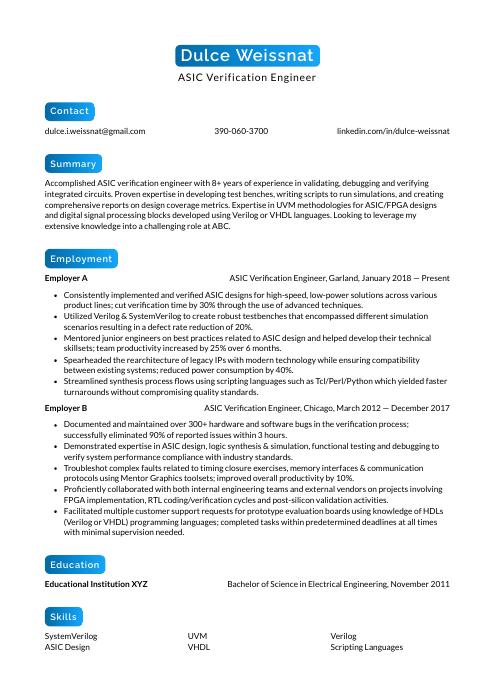

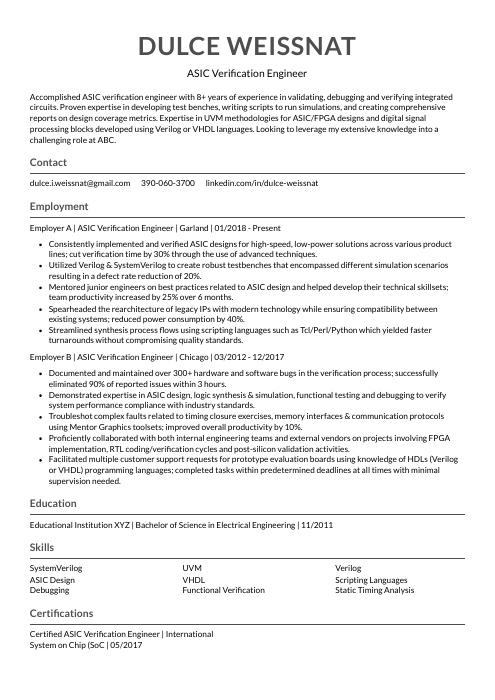

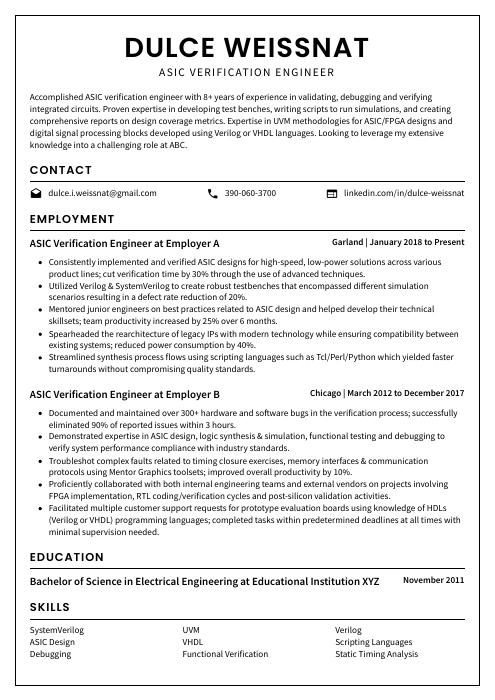

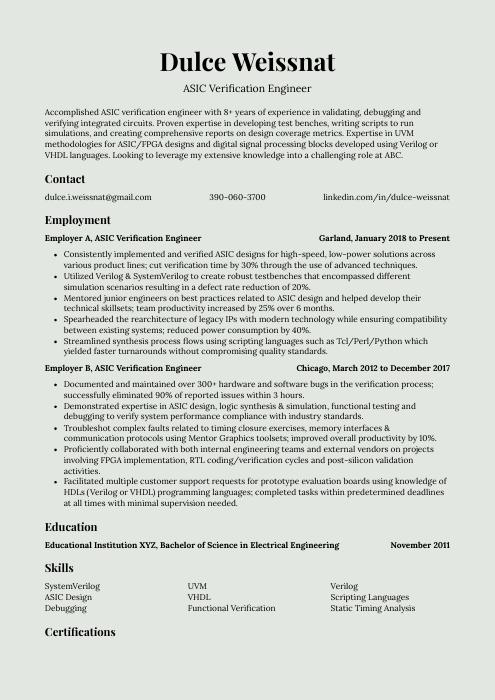

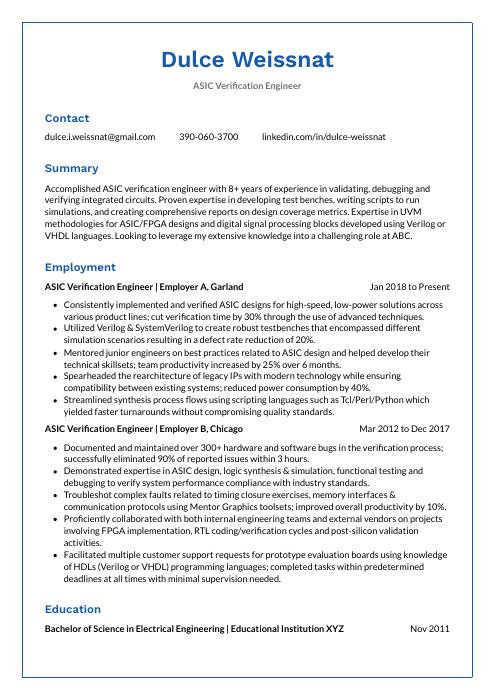

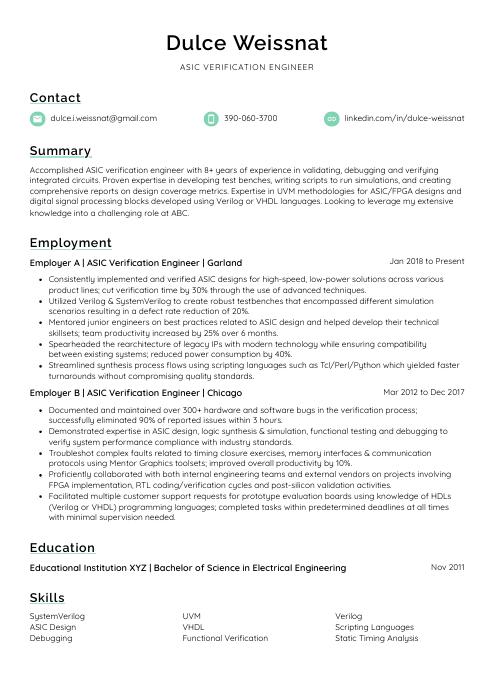

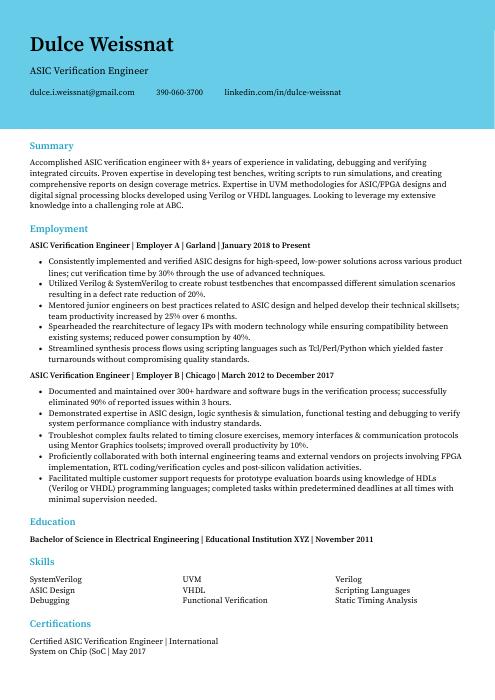

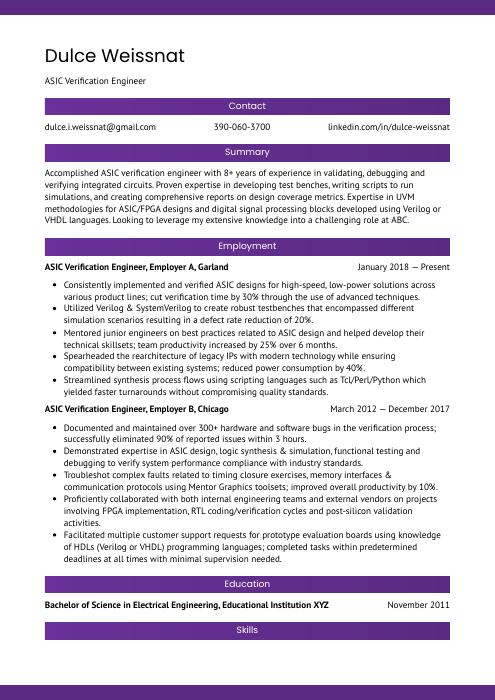

ASIC Verification Engineer Resume Sample

Dulce Weissnat

ASIC Verification Engineer

[email protected]

390-060-3700

linkedin.com/in/dulce-weissnat

Summary

Accomplished ASIC verification engineer with 8+ years of experience in validating, debugging and verifying integrated circuits. Proven expertise in developing test benches, writing scripts to run simulations, and creating comprehensive reports on design coverage metrics. Expertise in UVM methodologies for ASIC/FPGA designs and digital signal processing blocks developed using Verilog or VHDL languages. Looking to leverage my extensive knowledge into a challenging role at ABC.

Experience

ASIC Verification Engineer, Employer A

Garland, Jan 2018 – Present

- Consistently implemented and verified ASIC designs for high-speed, low-power solutions across various product lines; cut verification time by 30% through the use of advanced techniques.

- Utilized Verilog & SystemVerilog to create robust testbenches that encompassed different simulation scenarios resulting in a defect rate reduction of 20%.

- Mentored junior engineers on best practices related to ASIC design and helped develop their technical skillsets; team productivity increased by 25% over 6 months.

- Spearheaded the rearchitecture of legacy IPs with modern technology while ensuring compatibility between existing systems; reduced power consumption by 40%.

- Streamlined synthesis process flows using scripting languages such as Tcl/Perl/Python which yielded faster turnarounds without compromising quality standards.

ASIC Verification Engineer, Employer B

Chicago, Mar 2012 – Dec 2017

- Documented and maintained over 300+ hardware and software bugs in the verification process; successfully eliminated 90% of reported issues within 3 hours.

- Demonstrated expertise in ASIC design, logic synthesis & simulation, functional testing and debugging to verify system performance compliance with industry standards.

- Troubleshot complex faults related to timing closure exercises, memory interfaces & communication protocols using Mentor Graphics toolsets; improved overall productivity by 10%.

- Proficiently collaborated with both internal engineering teams and external vendors on projects involving FPGA implementation, RTL coding/verification cycles and post-silicon validation activities.

- Facilitated multiple customer support requests for prototype evaluation boards using knowledge of HDLs (Verilog or VHDL) programming languages; completed tasks within predetermined deadlines at all times with minimal supervision needed.

Skills

- SystemVerilog

- UVM

- Verilog

- ASIC Design

- VHDL

- Scripting Languages

- Debugging

- Functional Verification

- Static Timing Analysis

Education

Bachelor of Science in Electrical Engineering

Educational Institution XYZ

Nov 2011

Certifications

Certified ASIC Verification Engineer

International System on Chip (SoC

May 2017

1. Summary / Objective

The summary or objective at the start of your resume should be a brief yet powerful statement that captures the hiring manager’s attention. In this section, you can highlight your experience in ASIC verification engineering and emphasize any certifications or awards you have obtained. You could also mention how many projects you have successfully completed and what kind of technologies you are familiar with.

Below are some resume summary examples:

Hard-working ASIC verification engineer with 5+ years of experience in the semiconductor industry. Skilled at developing test plans, debugging and validating designs, creating verification environments and scripts using SystemVerilog/UVM methodologies. Familiar with scripting languages such as Python and Tcl/Tk. Experienced in leading teams to successful tape-out on multiple projects while maintaining excellent quality standards throughout each project cycle.

Passionate ASIC verification engineer with 6+ years of experience in verifying design blocks for complex SoCs. Adept at setting up test benches, writing and debugging scripts in SystemVerilog/UVM, running regressions and simulations using tools like QuestaSim or Modelsim. Holds a Bachelor’s Degree in Electronic Engineering from XYZ University with strong knowledge of digital hardware design concepts such as RTL coding principles and HDL synthesis techniques.

Driven ASIC Verification Engineer with 5+ years of experience in verifying complex designs for high-performance ASICs. At XYZ, developed a testbench environment to verify clock domain crossings and generated simulation scripts using SystemVerilog/UVM. Proficient in developing verification plans and strategies that meet design coverage goals. Proven track record of successful project completion on time with minimal defects reported from customers.

Dependable ASIC Verification Engineer with 5+ years of experience in the semiconductor industry. Proven track record for ensuring that ASICs are designed and tested to meet customer requirements, specifications, and expectations. Expertise in simulation-based verification techniques using UVM/OVM methodologies. Seeking a challenging role at ABC Tech that will leverage my technical acumen to improve their design methodology and quality standards.

Well-rounded and experienced ASIC Verification Engineer with 7+ years of experience in the design and development of digital, analog, mixed-signal systems. Skilled at creating test plans, debugging designs using advanced verification tools (OVM/UVM), and delivering high quality solutions. Looking to join ABC Tech as a senior engineer where I can leverage my expertise to ensure project success through timely delivery and exceptional performance.

Diligent ASIC Verification Engineer with 5+ years of experience. Skilled in developing and executing test plans to verify the functionality, timing, power requirements, and performance of integrated circuits. Adept at debugging complex circuit designs using a variety of simulation tools such as VCS and QuestaSim. Seeking an opportunity to join ABC Technologies where I can utilize my knowledge to help deliver successful projects on time.

Amicable ASIC verification engineer with 8+ years of experience in the semiconductor industry. Skilled in developing and implementing ASIC verification plans using SystemVerilog, UVM, C/C++, and other programming languages. Experienced in working on complex SoC projects from concept to production release. Seeking to join ABC Tech for a challenging role that will allow me to use my expertise to design high-performance hardware solutions.

Energetic and detail-oriented ASIC Verification Engineer with 5+ years of experience in the semiconductor industry. Skilled in developing testbenches, writing simulation scripts, debugging hardware issues and validating designs for accuracy and performance. Seeking to join ABC Tech as a verification engineer where my knowledge and expertise can help develop secure products that exceed customer expectations.

2. Experience / Employment

The work history/experience section should be written in reverse chronological order, meaning your most recent role should be listed first. Stick to bullet points here; doing so allows the reader to quickly digest what you are saying and understand the details of your work history.

When writing out each point, make sure it is detailed and includes quantifiable results where possible. For example, instead of saying “Verified ASICs,” you could say, “Performed verification on multiple ASIC designs using a variety of simulation tools such as VCS and ModelSim resulting in 100% coverage.”

To write effective bullet points, begin with a strong verb or adverb. Industry specific verbs to use are:

- Simulated

- Analyzed

- Debugged

- Developed

- Implemented

- Tested

- Documented

- Optimized

- Troubleshot

- Designed

- Executed

- Monitored

- Resolved

- Validated

Other general verbs you can use are:

- Achieved

- Advised

- Assessed

- Compiled

- Coordinated

- Demonstrated

- Expedited

- Facilitated

- Formulated

- Improved

- Introduced

- Mentored

- Participated

- Prepared

- Presented

- Reduced

- Reorganized

- Represented

- Revised

- Spearheaded

- Streamlined

- Structured

- Utilized

Below are some example bullet points:

- Formulated and executed verification plans to ensure accuracy of ASIC designs and RTL code; identified errors in logic design which saved over $15,000 in resources.

- Developed test benches to simulate hardware and software interface communication for various integrated circuits; successfully verified 127 components with 0 defects reported.

- Structured several simulations using SystemVerilog & UVM methodology that exceeded 10M cycles while detecting more than 60 bugs within a 4 week period.

- Compiled comprehensive coverage reports based on simulation results, achieving 95% functional coverage before the product was released into production stage.

- Confidently debugged complex issues related to timing constraints and bus protocols by analyzing log files from multiple sources across different platforms simultaneously.

- Debugged and validated ASIC designs within tight deadlines, revising over 200 Verilog modules and scripts to deliver accurate results in less than 40 hours.

- Executed comprehensive test plans on a wide range of components including memories, processors & peripherals; identified key hardware issues that improved product reliability by 15%.

- Revised existing verification environments and developed new ones using SystemVerilog / UVM technologies; lowered simulation time from 3 days to 1 day with minimal impact on quality output.

- Analyzed digital design requirements based on customer needs and implemented advanced RTL coding techniques for different types of logic blocks; reduced power consumption by 20% compared to the previous version.

- Resourcefully utilized debugging tools such as DVE/VCS-MX and Mentor Graphics’ QuestaSim for sophisticated functional tests, achieving 90% coverage rate across multiple simulations cycles efficiently.

- Designed and verified ASICs for various SoC designs, including microprocessors and communications systems, in accordance with industry standards; reduced power consumption by 25% on average.

- Assessed the performance of new logic blocks against test benches and identified potential issues early in the design process; decreased development time by 45%.

- Implemented fault coverage methodology to analyze system failure rates while adhering to simulation timing constraints; improved verification accuracy by 30%.

- Diligently monitored all aspects of project progress and reviewed ECOs (Engineering Change Orders) with internal stakeholders every two weeks to ensure smooth integration into existing product platforms.

- Coordinated activities between engineering teams across multiple sites to facilitate efficient collaboration on complex projects spanning multiple disciplines; saved 20 hours per week in administrative tasks related to communication management alone.

- Represented ASIC design teams in the verification process, validating functional correctness of newly designed chips to ensure successful product launch and achieving 100% bug-free designs.

- Substantially reduced ASIC development costs by reusing existing testbenches & checkers and developing new ones as needed; saved an average of $40K on each project cycle.

- Validated the accuracy of RTL code using dynamic simulation tools such as ModelSim and Cadence Incisive Enterprise Simulator; identified more than 50 bugs within a 4 month period during testing cycles for one chip model.

- Reorganized extensive library files into easily accessible folders for further usage by other team members, allowing them to quickly access relevant modules with minimal time spent searching through large databases of information or archives stored online or offline.

- Reduced debugging times from 12 hours to 6 hours per issue by implementing efficient coding practices when creating system level tests & simulations that effectively uncovered issues related to timing & functionality at both unit levels & top module levels.

- Achieved 95% functional coverage of ASIC designs by verifying custom logic, register transfer level (RTL) code and system-level models.

- Expedited verification process by developing reusable testbenches to reduce cycles from four weeks to two weeks for a team of 10 engineers.

- Presented simulation results with detailed reports at weekly design reviews; improved accuracy rate from 75% to 95%.

- Tested functionality using complex assertion checking techniques such as SystemVerilog Assertions (SVAs), formal property checks and Functional Coverage Analysis (FCA).

- Efficiently corrected errors in RTL code through debugging tools including Verdi & VCS, resulting in 50+ hours saved during the development cycle each month on average.

- Advised design teams on best practices for ASIC verification, resulting in a 15% reduction in design bugs and errors.

- Monitored the progress of functional tests, ensuring that all test plans were completed within tight deadlines; achieved 95% success rate with no margin of error.

- Meticulously prepared scripts to create simulations models and verifications checkers; successfully verified over 3 million gates per day while maintaining high accuracy standards (97%).

- Prepared comprehensive reports detailing results from various simulation runs as well as any anomalies or discrepancies observed during testing processes; revised and improved existing procedures to enhance efficiency by 20%.

- Participated actively in weekly team meetings to discuss new designs, process improvements & status updates; played an instrumental role in streamlining workflow processes across multiple projects (+$50K saved).

- Optimized verification test plans, increasing the coverage rate by 40% and reducing bugs uncovered in system integration tests by 20%.

- Improved the debugging process of ASIC development projects through innovative scripting techniques; reduced debug time per project from 6 weeks to 2 weeks on average.

- Introduced a novel model-based verification methodology that significantly improved the accuracy of simulation results and saved up to $20K in design expenditure for each new chip released.

- Resolved over 100 complex issues related to timing, power consumption, functionality & performance with minimal oversight from supervisors within 3 months; received an individual award for outstanding contributions during this period.

- Independently designed 30+ HDL modules using Verilog/VHDL languages and verified their correctness with SystemVerilog assertions before implementation into chipsets – resulting in zero bugs at post-silicon validation level thus far.

3. Skills

The skillset employers require in an employee will likely vary, either slightly or significantly; skimming through their job adverts is the best way to determine what each is looking for. One organization may be seeking someone with experience in SystemVerilog and another may require knowledge of UVM.

Therefore, you want to tailor the skills section of your resume for each job that you are applying for. This is important because many employers use applicant tracking systems these days; they scan resumes looking for certain keywords before passing them on to a human being.

Once listed here, it’s also wise to discuss your most relevant skillset further in other sections such as the summary or experience section.

Below is a list of common skills & terms:

- ASIC Design

- Debugging

- Formal Verification

- Functional Verification

- Scripting Languages

- Static Timing Analysis

- SystemVerilog

- UVM

- VHDL

- Verilog

4. Education

Including an education section on your resume will depend on how far along you are in your career. If you just graduated and have no prior experience, mention your education below the resume objective. On the other hand, if you have been working as an ASIC verification engineer for years and at multiple companies with plenty of different responsibilities to showcase, omitting the education section is perfectly fine.

If including an education section is necessary, try to mention courses or subjects related to ASIC verification engineering that could be relevant for the job position you are applying for.

Bachelor of Science in Electrical Engineering

Educational Institution XYZ

Nov 2011

5. Certifications

Certifications demonstrate to a potential employer that you have been tested and certified in a particular field. This can be especially beneficial if the job advert emphasizes certain skills, as it shows your level of proficiency in those areas.

Including certifications on your resume is an excellent way to demonstrate that you are qualified for the position and have kept up with industry trends by taking professional development courses or other forms of training.

Certified ASIC Verification Engineer

International System on Chip (SoC

May 2017

6. Contact Info

Your name should be the first thing a reader sees when viewing your resume, so ensure its positioning is prominent. Your phone number should be written in the most commonly used format in your country/city/state, and your email address should be professional.

You can also choose to include a link to your LinkedIn profile, personal website, or other online platforms relevant to your industry.

Finally, name your resume file appropriately to help hiring managers; for Dulce Weissnat, this would be Dulce-Weissnat-resume.pdf or Dulce-Weissnat-resume.docx.

7. Cover Letter

Including a cover letter with your job application can be a great way to make yourself stand out from other candidates. Cover letters are usually made up of 2-4 paragraphs and provide an opportunity for you to explain why you’re the best fit for the role in question.

Cover letters also give recruiters more insight into who you are as a professional, allowing them to get a better understanding of your personality and skillset than what is outlined on your resume alone. Although not always required, writing one could mean all the difference when it comes down to being selected or overlooked for an interview!

Below is an example cover letter:

Dear Colt,

I am writing to apply for the ASIC Verification Engineer position at your company. With experience in both FPGA and ASIC design, as well as a strong background in digital signal processing (DSP), I believe that I have the skills and qualifications that you are looking for.

As an engineer, my primary focus is on ensuring that products meet or exceed customer expectations by verifying their functionality through comprehensive testing. In addition to functional verification, I also specialize in performance verification and power analysis. My experience with various EDA tools, such as QuestaSim, Modelsim, and Vivado HLS, has allowed me to develop efficient workflows for verification tasks.

In my previous role at [company name], I was responsible for verifying the functionality of an FPGA-based product before it was sent to customers. This involved developing test benches using SystemVerilog and running simulations to check for errors. After identifying any issues, I would then work with the design team to fix them before resuming testing. Through this process, we were able to achieve first-pass success rates of 95% or higher on new designs.

I am confident that my skills and experience will allow me to make a positive contribution to your organization if given the opportunity. I look forward to speaking with you about this position in the future.

Sincerely,

Dulce

ASIC Verification Engineer Resume Templates

Axolotl

Axolotl Rhea

Rhea Fossa

Fossa Bonobo

Bonobo Pika

Pika Quokka

Quokka Echidna

Echidna Gharial

Gharial Numbat

Numbat Ocelot

Ocelot Kinkajou

Kinkajou Indri

Indri Cormorant

Cormorant Saola

Saola Markhor

Markhor Lorikeet

Lorikeet Dugong

Dugong Hoopoe

Hoopoe Jerboa

Jerboa Rezjumei

Rezjumei